2024/5/27 16:47:38

2024/5/27 16:47:38

75

75

1 Features

• Available in the Texas Instruments NanoStar™ Package

• Low Static-Power Consumption (ICC = 0.9 µA Maximum)

• Low Dynamic-Power Consumption (Cpd = 4 pF Typical at 3.3 V)

• Low Input Capacitance (CI = 1.5 pF Typical)

• Low Noise

– Overshoot and Undershoot < 10% of VCC

• Input-Disable Feature Allows Floating Input Conditions

• Ioff Supports Partial-Power-Down Mode Operation

• Input Hysteresis Allows Slow Input Transition and Better Switching Noise Immunity at Input

• Wide Operating VCC Range of 0.8 V to 3.6 V

• 3.6-V I/O Tolerant to Support Mixed-Mode Signal Operation

• tpd = 4.6 ns Maximum at 3.3 V

2 Applications

• Audio Dock: Portable

• BluRay™ Players and Home Theaters

• Personal Digital Assistant (PDA)

• Power: Telecom/Server AC/DC Supply: Single Controller: Analog and Digital

• Solid-State Drive (SSD): Client and Enterprise

• TV: LCD/Digital and High-Definition (HDTV)

• Tablet: Enterprise

• Wireless Headsets, Keyboards, and Mice

3 Description

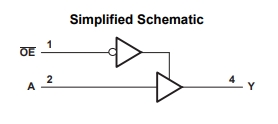

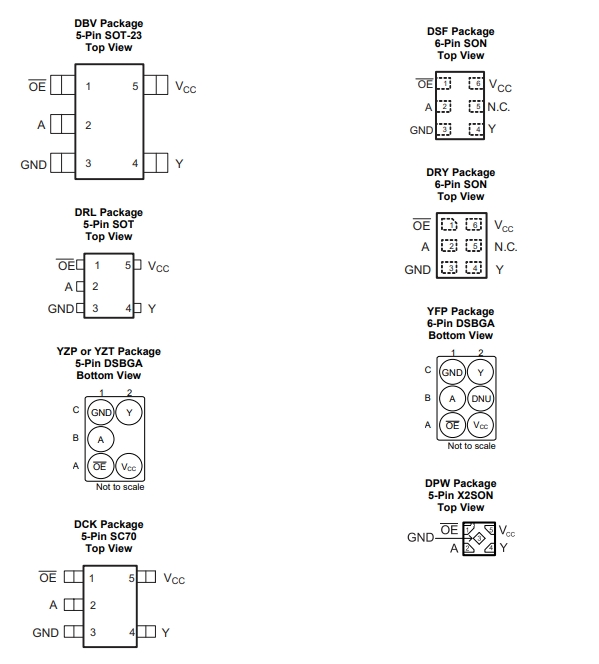

The SN74AUP1G125 bus buffer gate is a single line driver with a 3-state output. The output is disabled when the output-enable (OE) input is high. This device has the input-disable feature, which allows floating input signals.

To ensure the high-impedance state during power up or power down, OE must be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

热门型号

热门资讯

20万现货SKU

品类不断扩充

科技智能大仓储

4小时快速交货

仅从原厂和代理商进货

每一颗料均可原厂追溯

明码标价节省时间成本

一站式采购正品元器件