2024/6/27 17:07:03

2024/6/27 17:07:03

487

487

· Internal Look-Ahead for Fast Counting

· Carry Output for n-Bit Cascading

· Synchronous Counting

· Synchronously Programmable

· SCR-Latchup-Resistant CMOS Process and Circuit Design

· Exceeds 2-kV ESD Protection per MIL-STD-883, Method 3015

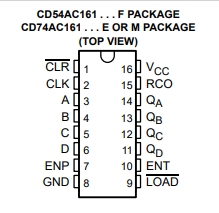

description/ordering information

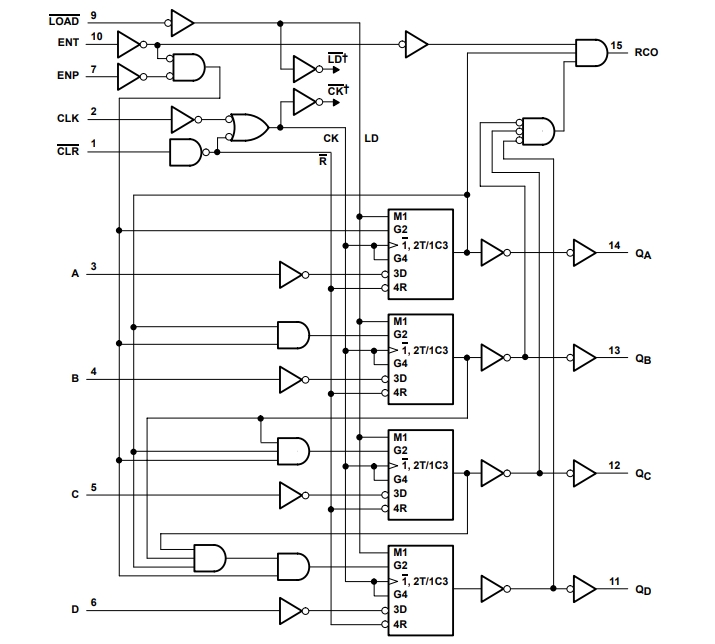

The ’AC161 devices are 4-bit binary counters. These synchronous, presettable counters feature an internal carry look-ahead for application in high-speed counting These devices are fully programmable; that is, they can be preset to any number between 0 and 9 or 15. Presetting is synchronous; therefore, setting up a low level at the load input disables the counter and causes the outputs to agree with the setup data after the next clock pulse, regardless of the levels of the enable inputs.

The clear function is asynchronous. A low level at the clear (CLR) input sets all four of the flip-flop outputs low, regardless of the levels of the CLK, load (LOAD), or enable inputs.

The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without additional gating. Instrumental in accomplishing this function are ENP, ENT, and a ripple-carry output (RCO). Both ENP and ENT must be high to count, and ENT is fed forward to enable RCO. Enabling RCO produces a high-level pulse while the count is maximum (9 or 15, with QA high). This high-level overflow ripple-carry pulse can be used to enable successive cascaded stages. Transitions at ENP or ENT are allowed, regardless of the level of CLK.

The counters feature a fully independent clock circuit. Changes at control inputs (ENP, ENT, or LOAD) that modify the operating mode have no effect on the contents of the counter until clocking occurs. The function of the counter (whether enabled, disabled, loading, or counting) is dictated solely by the conditions meeting the stable setup and hold times.

热门型号

热门资讯

20万现货SKU

品类不断扩充

科技智能大仓储

4小时快速交货

仅从原厂和代理商进货

每一颗料均可原厂追溯

明码标价节省时间成本

一站式采购正品元器件